台积电近日在线上研讨会上透露了有关于先进制程的大量资讯,目前刚量产的5纳米制程良率已经迅速超过7纳米,对于苹果A14X芯片以及AMD Zen 4处理器都是非常好的消息。

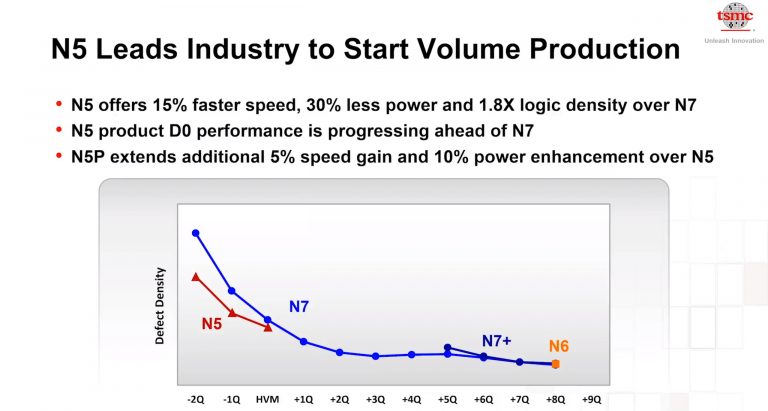

通常半导体制程良率是随着时间而下降,并获得更高的产量,也就是学习曲线的概念。不过台积电表示,尽管5纳米是更先进的制程,但学习曲线表现比7纳米更好,使量产非常顺利,而5纳米强化版制程N5P也即将于明年开始量产,性能将再度提高5%,或功耗降低10%。

基本上只要缺陷数低于0.5/cm 2就算是合格的良率,目前已相当成熟的7纳米制程0.09/cm 2,但才刚量产不久的5纳米制程良率就已达到了0.1/cm 2,显示出过往更好的学习曲线,这可能主是得益于EUV技术的应用,减少了工艺步骤,原本需要4步DUV如今EUV能一次完成,降低了生产风险,如此下一季5纳米良率就将比7纳米更好。

(Source:TSMC)

目前来看5纳米将会给台积电带来更强的竞争力,不仅如此,台积电还提供了最新N4工艺的预览,N4除了通过减少掩模层来简化工艺外,还提供了一条直接迁移路径,可以全面相容5纳米设计生态,预期将于明年底试产,2022年实现量产。

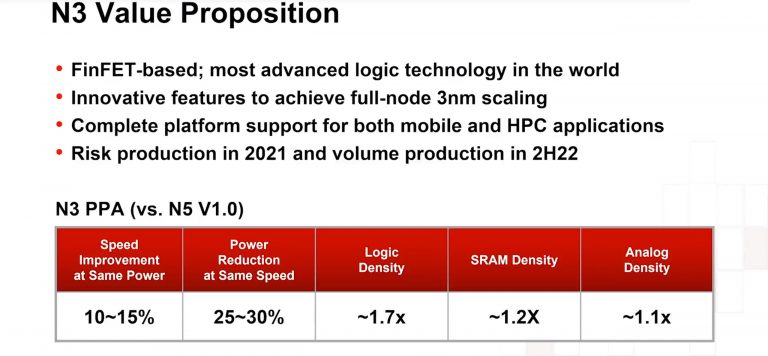

而台积电下一代的N3工艺将成为世界上最先进的逻辑技术,又会再度出现性能的飞跃与5纳米相比将实现全节点的技术进步,性能再度提高15%、功耗降低30%、逻辑密度提高70%。但值得注意的是,3纳米仍然会是FinFET,这点倒是令市场相当意外,预计要到2纳米才会采用GAA。

(Source:TSMC)

当然面对质疑,台积电也表示,经过与客户的协商,3纳米制程预期的成本及性能表现已受到广泛的支持。尽管三星宣称在3纳米将使用GAA,但台积电仍相当胸有成竹。当然台积电仍在持续探索3纳米以下的技术,例如纳米碳管等新材料的应用,不过目前来看单一晶体管的性能提升已渐趋有限,需要更好的设计才能达到更高的效率。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。